Hi,

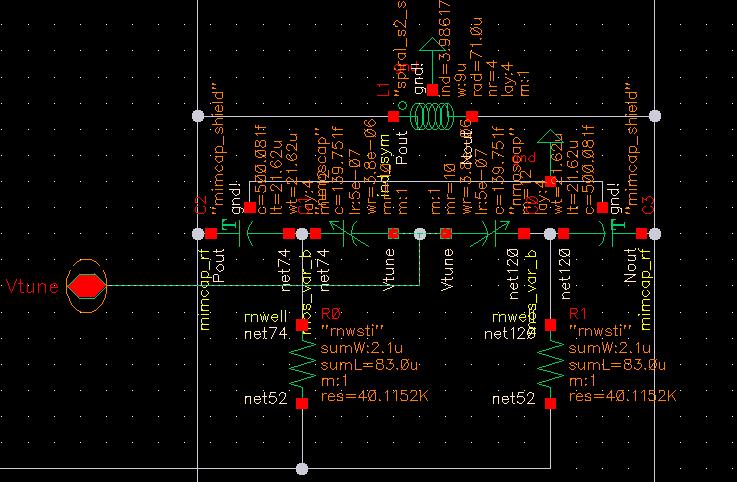

I am working in a Δ-Σ Fractional-N Frequency Synthesizers, I have a question about the connection of the filter and VCO in the circuit. The varactor of the VCO is AMOS as shown in Fig.1, the Vtune Voltage is directly connected to one port of the AMOS.

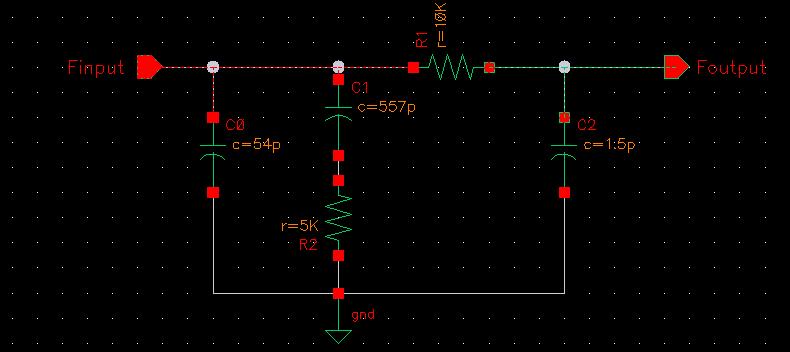

The loop filter is off-chip and 3order as shown in Fig.2.

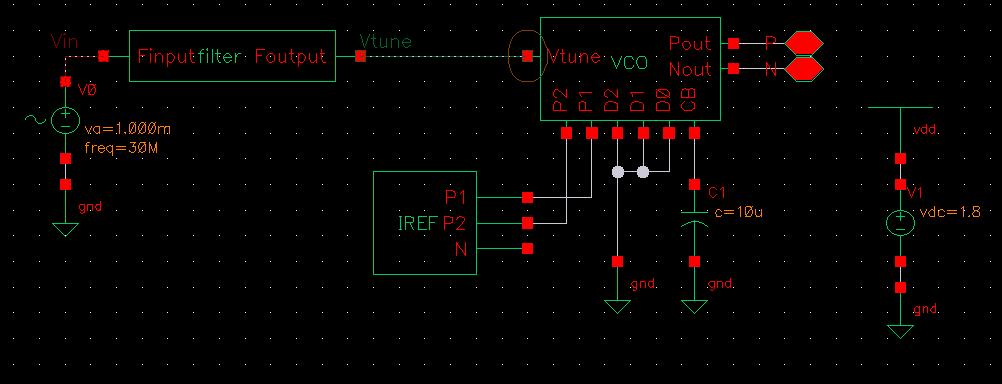

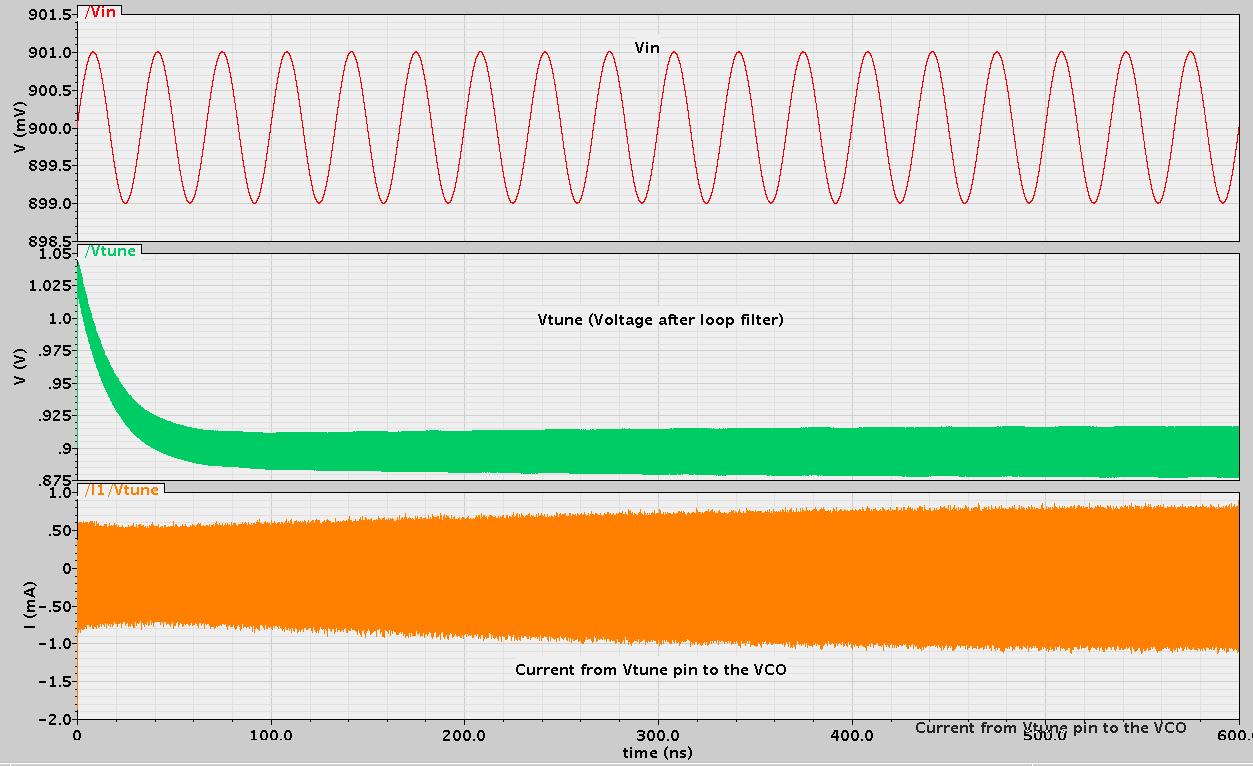

In the total circuit system connection, I connect the Filter and VCO directly, but, I found, the Vtune Voltage after the loop filter will be distorted, and a large current flow in to/out from the VCO, and this makes a large spurious tones to the Voltage signal, and makes it not stable. The voltage added to the filter (Vin), voltage after the filter (Vtune) and the current into the VCO are shown in Fig. 3

And I think I only need the Voltage value in VCO tune, the Current is unwanted, and I should removal the current, is that right?

I try to add a large resistor between the filter and the VCO to limit the current, and the VCO work well, but what I worry is that is the method right? what value the resistor shoule be and shoule it be off-chip? and is the resistor added here will effect the loop filter zero/pole? Or should I make any change in the VCO tune voltege input pin design, please?

Thank you!

Best regards!

Home

Home

Help

Help

Search

Search

Login

Login

Register

Register

PM to admin

PM to admin