# A Frequency Compensation Scheme for LDO Voltage Regulators

Chaitanya K. Chava, Member, IEEE, and José Silva-Martínez, Senior Member, IEEE

Abstract—A stable low dropout (LDO) voltage regulator topology for low equivalent series resistance (ESR) capacitive loads is presented. The proposed scheme generates a zero internally instead of relying on the zero generated by the load capacitor and its ESR combination for stability. It is demonstrated that this scheme realizes robust frequency compensation, facilitates the use of multilayer ceramic capacitors for the load of LDO regulators, and improves transient response and noise performance. Test results from a prototype fabricated in AMI 0.5- $\mu$ m CMOS technology provide the most important parameters of the regulator viz., ground current, load regulation, line regulation, output noise, and start-up time.

Index Terms—Frequency compensation, linear regulators, low dropout (LDO) regulator, LDO stability, power management.

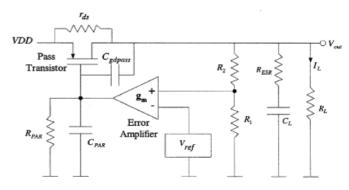

Fig. 1. Typical LDO voltage regulator.

# III. CAPACITIVE FEEDBACK FOR FREQUENCY COMPENSATION

The basic idea behind the capacitive feedback is to introduce a left hand plane zero in the feedback loop that would replace the zero generated by ESR of the output capacitor. We would then have the advantages of precisely controlling the zero location and minimize the overshoots. Prior art using the idea of capacitive feedback and internal zero compensation can be found in [11]-[13]. In [11], the goal was reached by adding a pole-zero pair with zero at lower frequency than the pole. This pole-zero pair improves the phase margin, but, a drastic improvement in phase margin can be obtained by adding only a zero. [12] presents a solution in which an internal zero is added by using a series resistor and capacitor combination connected to the output of error amplifier. In this solution, the resistor and capacitor pair would consume large silicon area as the zero should occur at very low frequencies to achieve the desired compensation. The capacitor added to generate the zero also reduces the frequency of the pole at the output of the error amplifier. The proposed method starts with the addition of a pole-zero pair as in [11] and proceeds toward eliminating the pole from the pole-zero pair.

To introduce capacitive feedback, a capacitor can be added to the original LDO configuration, [Fig. 3(a)] to provide a highfrequency bypass path for the loop gain. This capacitor produces a pole–zero pair in the open-loop transfer function as follows:

$$H(s) = \frac{A_0 \left(1 + \frac{s}{\omega_{Z1}}\right)}{\left(1 + \frac{s}{\omega_{P1}}\right) \left(1 + \frac{s}{\omega_{P2}}\right) \left(1 + \frac{s}{\omega_{P3}}\right)}.$$

(7)

$A_0$ ,  $\omega_{P1}$ , and  $\omega_{P2}$  are defined in (2), (4), and (5).  $\omega_{Z1}$  and  $\omega_{P3}$  are given by

$$\omega_{Z1} = \frac{1}{R_2 C_1} \tag{8}$$

$$\omega_{P3} = \frac{1 + \frac{R_2}{R_1}}{R_2 C_1}.$$

(9)

Although  $C_1$  introduces the required zero,  $\omega_{P3}$  is not far away from the zero since  $R_2/R_1$  is around 1.33. The topology has to be modified so as to eliminate  $\omega_{P3}$  without affecting the zero. Fig. 3(b) shows how the capacitor is split into two frequency-dependent voltage-controlled current sources (VCCS) and grounded capacitors. The capacitor  $C_1$  and the VCCS connected to  $v_{out}$  do not significantly alter the voltage at that node since  $C_L$  is of several microfarads, whereas  $C_1$  is on the order of few picofarads. It should also be noted that the capacitor connected to  $v_x$  is responsible for the additional pole  $\omega_{P3}$ ; therefore it is eliminated to arrive to the final configuration of Fig. 4. This configuration generates the required zero; the LDO becomes a two-loop system. The VCCS is a differentiator that increases the loop gain at high frequencies.

The loop gain transfer function of the regulator with this configuration has one zero and two poles given by

$$\omega_{Z1} = \frac{1}{R_2 C_1}$$

(10)

$$\omega_{\text{P1}} = \frac{1}{(r_{ds}|R_L||(R_1 + R_2))\left(C_L - \frac{C_1}{\beta}\right)}$$

(11)

where  $\beta=1+R_2/R_1$  and  $\omega_{\rm P2}$  is given by (4). The loop transfer function of the proposed regulator is similar to that of conventional regulator except that the product of  $C_1$  and feedback resistor  $R_2$  generates the left half plane zero instead of the output capacitor's ESR. It should be noted that the location of the pole  $\omega_{\rm P1}$  is almost not altered by  $C_1$  as it is primarily dependent on  $C_L$ . The designer can accurately control the frequency of the zero. Other advantages will be evident in the next sections. It would be of some interest to note that the proposed compensation scheme works only with low ESR capacitors as co-existence of VCCS generated zero and ESR generated zero at low frequencies might make loop gain undesirably high.

# A. Design Considerations for the VCCS

The transistor-level design challenge lies in realizing the frequency dependent VCCS with minimum die area and minimum power consumption while retaining the VCCS characteristics up to crossover frequency of the loop transfer function. The simplest realization of this circuit is shown in Fig. 5(a). The bias current  $I_B$  can be selected to meet the objective of minimal standby current; the limit is however determined by the frequency of its parasitic pole determined by  $g_{m1}/C_1$ . The overall small-signal transconductance is given by (12)

$$\frac{i_{\text{out}}}{v_{\text{out}}} = \frac{sC_1}{1 + \frac{C_1}{g_{m1}}s}$$

(12)

Hand calculations and simulated results show us that the parasitic pole occurs at around 400 KHz for  $I_B = 0.5 \mu A$  and  $C_1 = 5$  pf. The current mirror introduces another parasitic pole but it is located at higher frequencies because of the small parasitic capacitors. To push the parasitic pole beyond 1 MHz for  $C_1 = 25$  pf (required for the proper location of the zero), we need to improve the effective  $g_{m1}$ . Increasing the small-signal transconductance by increasing the bias current drastically increases the power consumption  $(g_m)$  scales proportional to the square root of bias current). Therefore, alternate  $G_m$  enhancement techniques should be explored. The impedance zin seen from the source of M1 is roughly equal to  $1/g_{m1}$ . Fig. 5(b) modifies the basic topology using an operational transconductance amplifier (OTA) in feedback for  $G_m$  enhancement. The effective transconductance  $G_m$  is given by the product of the voltage gain of the auxiliary OTA and the small-signal transconductance of  $M_x$  ( $G_m = A_{VOTA} g_{mx}$ ). The impedance seen from the source of  $M_x$  is given by the following:

$$z_{\rm in} \cong \left(\frac{1}{g_{m \text{ aux}} g_{mx} r_{\rm aux}}\right) \left(\frac{1 + s(r_{\rm aux} C_{\rm aux})}{1 + \frac{C_{\rm aux}}{g_{m \text{ aux}}} s}\right)$$

(13)

where  $g_{m \text{ aux}}$  is the small-signal transconductance of the auxiliary amplifier. The input impedance is very small at low frequencies, collecting all current generated by  $C_1$ . It is mandatory to reduce as much as possible  $r_{\text{aux}}C_{\text{aux}}$  to extend the frequency capabilities of the circuit. At high frequencies, the input impedance increases up to  $1/g_{mx}$ ; if  $z_{\text{in}}| \ll 1/\omega C_1$  then, the circuit can properly drive  $C_1$ .

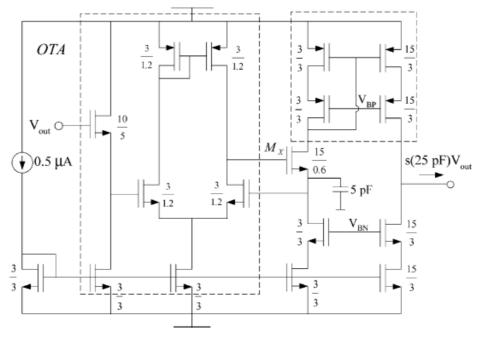

The transistor realization is shown in Fig. 6. The circuit consists of three parts. The first stage acts as a level-shifting buffer needed to down-shift the dc level which can be very close to the supply voltage due to LDO characteristics of the regulator. The next stage is  $M_x$  with  $G_m$  enhancing OTA in feedback. The third stage consists of a 1:5 current mirror and bias sources

Fig. 6. Transistor level implementation of VCCS with  $G_m$  enhancement.

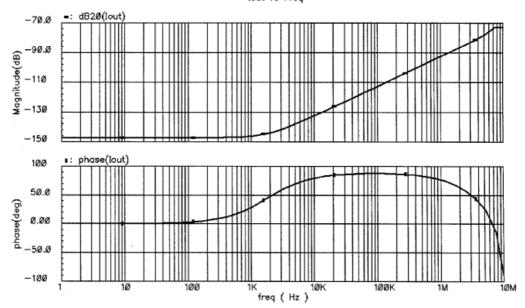

Fig. 7. Frequency response of the circuit shown in Fig. 6.

that together perform the function of pumping the ac current through output. We can take advantage of a multiplication factor in the current mirror to increase the effective capacitance from 5 to 25 pF. Cascode current mirror and cascode bias current sources (bias by proper dc voltages  $V_{\rm BP}$  and  $V_{\rm BN}$ ) are used such that offset current is not significant enough to upset the dc output voltage of the regulator. Transistor dimensions are such that  $g_{m~\rm aux}/C_{\rm aux}$  is beyond  $2\pi\times 5$  MHz. The total current consumed by this structure is 4  $\mu$ A. The circuit simulation is plotted in Fig. 7. We notice that VCCS characteristics are retained up to a frequency of 5 MHz.

### IV. SYSTEM LEVEL DESIGN CONSIDERATIONS

The two other components of the LDO voltage regulator loop are the pass transistor and the error amplifier. The important design consideration for the pass transistor is the dropout voltage. Increasing the size of the pass transistor lowers the dropout voltage for a particular output current, but wider pass transistor introduces higher input capacitance making it difficult to meet stability and slew rate requirements. The design presented in this paper uses a pass transistor of 6000  $\mu$ m/1  $\mu$ m that gives a maximum output current of 100 mA with a dropout voltage of

0.5 V. Minimum length is not used as it makes the transistor output impedance unacceptably low at high load currents.

The error amplifier design demands careful attention to meet the required loop gain, transient response and stability. Ideal requirements of the error amplifier are: 1) high dc gain to ensure high loop gain (typically  $> 60 \, \mathrm{dB}$ ) for all loads; 2) low output impedance to keep the pole at the input of the pass transistor at high frequencies; 3) positive rail output to turn off pass transistor when the load turns off; and 4) internal poles at significantly higher frequencies compared to the cross over loop frequency. High output impedance of the error amplifier pushes the pole at the input of the pass transistor ( $\omega_{P2}$ ) to lower frequencies.  $\omega_{P2}$  is pushed to higher frequencies by limiting the output impedance of the error amplifier; hence the use of a two-stage error amplifier is a must.

### A. Load Regulation

Load regulation characteristics are not symmetrical for increase and decrease in load current. In the proposed circuit, when load current is increased instantaneously, the load capacitor supplies the extra current and the capacitor voltage drops. This drop in output voltage is sensed by the feedback circuit which in turn pulls down the gate of the pMOS pass transistor thus turning it on and supplying the output current needed by the capacitor and load impedance. Since the compensating circuit is a differentiator, it helps increasing the loop feedback for fast output variations. On the other hand, if ESR is used, the instantaneous current flows through the resistor increasing further the overshoots at the LDO output, especially if large ESR is used.

When the load current is decreased instantaneously, the extra current from the output of the pass transistor charges the output capacitor to a higher than nominal voltage. The feedback loop reacts by switching the error amplifier to positive saturation limit thereby turning off the pass transistor. The excess charge on the output capacitor is discharged through the feedback resistors; hence the discharge time is large because R1 and R2 are in the range of hundreds of kilo ohms. The positive saturation voltage of the error amplifier needs to be close to the supply voltage since we need to turn off the pass transistor, whose subthreshold current could be substantial owing to its large size. An error amplifier with nMOS output buffer stage does not have high positive saturation voltage. One of the solutions [8] is to use an nMOS buffer with a low  $V_t$  nMOS transistor available in some expensive processes. A simpler solution is achieved in the current design by eliminating the buffer stage; the amplifier structure is shown in Fig. 8. A two-stage amplifier is used in order to have enough voltage swing at the output. Minimum dimensions are used in most of the transistors in order to reduce the capacitance at the output of the first stage. The parasitic capacitors at the output of the first stage of error amplifier are in the range of 50 fF, leading to a parasitic pole around 5 MHz for the worst corner simulation. Since unity gain frequency of the loop gain is below 1 MHZ this parasitic pole does not affect the overall compensation scheme. The error amplifier dc gain is around 60 dB.

### B. Line Regulation

At low frequencies, line regulation (power supply rejection) of the regulator is determined by the loop dc gain. Since the introduction of VCCS does not change the loop gain, the power supply rejection of the regulator is not adversely affected by the proposed scheme. High-frequency line regulation is not degraded since VCCS does not add any significant parasitic capacitance from supply voltage to the output.

### C. Start-Up Time

Start-up time of a regulator is important for the applications where power supervisory circuit frequently turns the regulator on and off. The proposed circuit has similar start-up time compared to the scheme with ESR generated zero, assuming that power supply is ramped up with a rise time of few microseconds. The speed limitation comes from the fact that the VCCS has an ideal behavior up to a few megahertz. For faster power-supply ramps, the start-up behavior could be slightly different for both cases depending upon high-frequency behavior of the VCCS.

## V. SIMULATED AND EXPERIMENTAL RESULTS

The LDO regulator is tested for  $R_1 = 120 \text{ k}\Omega$ ,  $R_2 = 160 \text{ k}\Omega$ ,  $V_{\text{ref}} = 1.2 \text{ V}$ ,  $V_{\text{DD}} = 3.3 \text{ V}$  and multilayer ceramic output capacitor  $C_L = 2.2 \ \mu\text{F}$  (Z5U class) with several bypass capacitors in the nF range placed in parallel to reduce high-frequency noise. The ESR of  $C_L$  is below  $100 \text{ m}\Omega$ . The dc output voltage of the regulator is 2.8 V. The ground current consumed by the LDO regulator is  $25 \ \mu\text{A}$ ;  $5 \ \mu\text{A}$  is consumed by the VCCS.

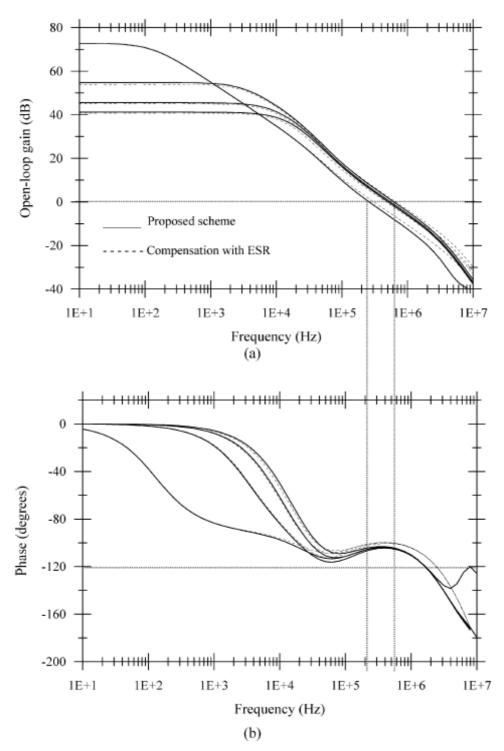

The LDO regulator was simulated and the open-loop gain results are shown in Fig. 9. The load current was changed from 100 mA ( $R_L \sim 28~\Omega$ ) to 1 mA ( $R_L \sim 2800~\Omega$ ) by using a nMOS transistor switch driven by an ideal voltage source; the setup is similar to the one used in [4]. The series resistance of ESR compensation is 2  $\Omega$ . The unity gain frequency is in the range of 250–650 kHz. The phase response is shown in Fig. 9(b); phase margin is better than 60° for all cases. Notice that the frequency response is quite similar for both topologies.

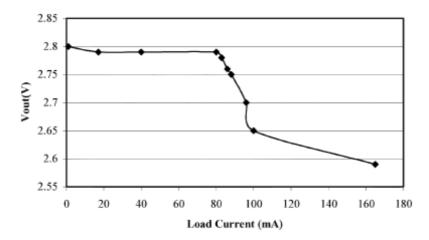

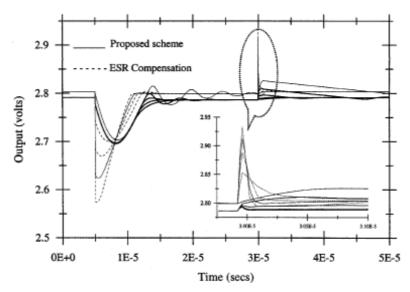

The integrated circuit micrograph of the regulator, designed in 0.5-μm CMOS technology and fabricated through the MOSIS educational program, is shown in Fig. 10. The pass transistor occupies most of the silicon area.  $C_1$  and the VCCS do not contribute to a significant increase in the overall area. The regulator's output voltage as the load current is varied from 1 to 160 mA is shown in Fig. 11. For testing the LDO and external current mirror was used, and its output impedance is heavily dependent of the amount of current. Loop gain increases further for very small currents (pass transistor go into subthreshold region and the output resistance of both pass transistor and load increase); error increases for large load currents leading to voltage deviations of around 10 mV for load currents greater than 20 mA. Another voltage drop in the output voltage occurs when the pass transistor goes into triode region thereby reducing the open-loop gain. The LDO's transient response for load pulsed currents of 1 mA and 100 mA has been extensively simulated. For the proposed scheme the compensating capacitor is varied from 0.5 to 7.5 pF (continuous curves). For the circuit using ESR, the resistance is varied in the range of  $0.1-2.5 \Omega$  (dashed curves); the results are shown in Fig. 12. For small ESR values, some parasitic oscillations are present due to the limited phase margin. For larger ESR, the oscillations disapear but the overshoot increases; clearly there is an unavoidable tradeoff between stability and overshoot. For the proposed scheme, the overshoot is little sensitive to the compensating capacitor. If the compensating capacitor is not large enough, some oscillations might appear in the transient response. Notice that the overshoot of the proposed scheme is less than 100 mV for all cases.

Fig. 9. LDO regulator open-loop gain. (a) Magnitude response. (b) Phase response. The load current is 1, 34, 67, and 100 mA.

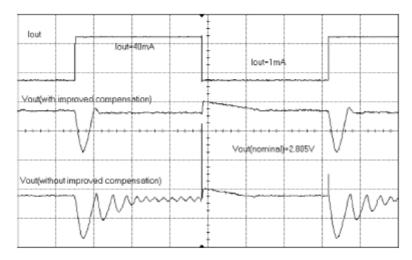

Fig. 11. Experimental LDO output voltage as function of the load current. The load regulation has also been experimentally tested. To probe the effects of the proposed technique toward stability, load regulation characteristics are taken with and without VCCS enabled. The experimental results are presented in Fig. 13. As the load current is increased from 1 to 40 mA, the output voltage drops immediately since the output capacitor gets discharged.

Fig. 12. LDO's transient response for load pulsed currents of 1 mA (0–5  $\mu s$  and 30–50  $\mu s$ ) and 100 mA (5–30  $\mu s$ ). For the proposed scheme  $C_1$  is 0.5, 2.5, 5, and 7.5 pF. For the ESR, the resistance is 0.1, 0.5, 1.5, and 2.5  $\Omega$ .

Fig. 13. Load regulation characteristics of the LDO regulator as output current is varied from 1 to 20 mA. (X-axis 50  $\mu$ s/div, Y-axis 50 mV/div).

The feedback loop responds to this drop in output voltage and the circuit is supposed to adjust to new loading conditions with the output voltage coming back to the nominal voltage. However, since we are using a low ESR output capacitor, instability is introduced and causes sustained oscillations as seen in the lower trace of Fig. 13. These oscillations are suppressed by activating the compensation scheme as seen in the middle trace. The settling time of the circuit is not very fast when the load current drops from 40 to 1 mA; the output capacitor discharges through feedback resistors giving a simple RC circuit response.

The stability of the proposed scheme is fully tested by applying a pulsed signal (±20 mV) on top of the 1.2-V reference voltage as shown in the top trace of Fig. 14. The LDO with the phase compensation (middle trace) is stable showing that the phase margin is good enough. The test results are also taken without activating the frequency compensation scheme to prove that instability present in the circuit is removed when the compensation scheme is used (Fig. 14 bottom trace).

The response of the regulator circuit to voltage spikes in the power supply is shown in Fig. 15. Line regulation tends to be worse for small load currents since these conditions result in lower bandwidth, therefore the zero is closer to the loop unity gain frequency. The power-supply regulation for a load current